| •        |    |

|----------|----|

| GENER    | ΑL |

| INSTRUME | NT |

SP0256A

### NARRATOR<sup>TM</sup> SPEECH PROCESSOR

#### **FEATURES**

- Natural Speech

- Stand Alone Operation with Inexpensive Support Components

- Wide Operating Voltage

- Word, Phrase, or Sentence Library, ROM Expandable

- Expandable to 491K of ROM Directly

- Simple Interface to Most Microcomputers or Microprocessors

- Supports L.P.C. Synthesis; Formant Synthesis; and Allophone Synthesis

#### GENERAL DESCRIPTION

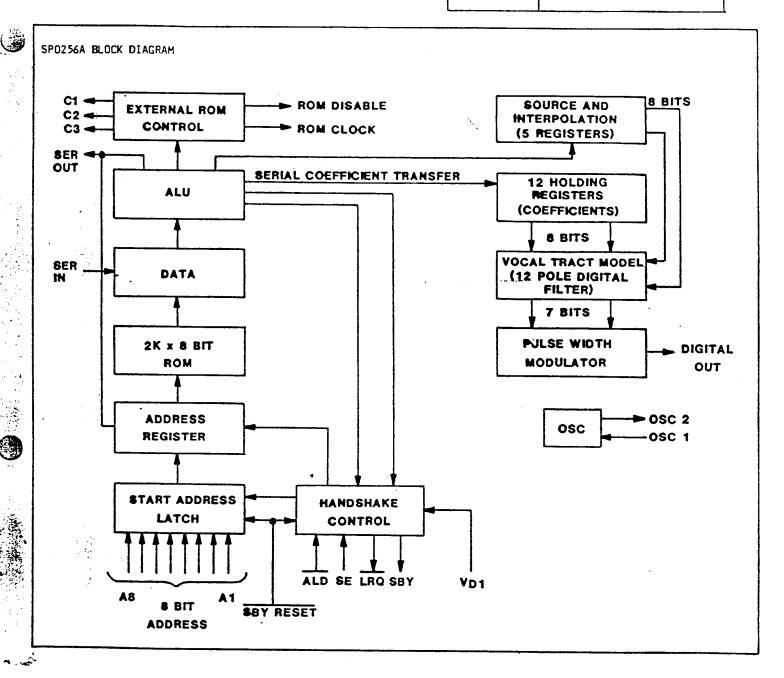

The SP0256A Speech Processor (SP) is a single chip N-Channel MOS\_LSI device that is able, using its stored program to synthesize speech or complex sounds.

The achievable output is equivalent to a flat frequency response ranging from 0 to 5%Hz, a dynamic range of 42dB, and a signal to noise ratio of approximately 35dB.

The SP0256A incorporates four basic functions:

- A software programable digital filter that can be made to model a VOCAL TRACT.

- A 16K ROM which stores both data and instuctions (THE PROGRAM).

- A MICROCONTROLLER which controls the data flow from the ROM to the digital filter, the assembly of the "word strings" necessary for linking speech elements together, and the amplitude and pitch information to excite the digital filter.

- A PULSE WIDIH MODULATOR that creates a digital output which is converted to an analog signal when filtered by an external low pass filter.

## ALLOPHONE BASED SPEECH PROCESSOR - SP0256A-AL2

One example of a preprogramed SP0256A is the AL2 pattern.

The SP0256A-AL2 is available preprogramed with a standard ROM Pattern containing 64 allophones. Through the concatenation of selected allophones

the user can construct any word in the English language, thereby providing an unlimited vocabulary.

A complete description of the SP0256A-AL2 is contained in the SP0256A-AL2 Data Sheet.

#### **APPLICATIONS**

- Telecommunications

- Appliances

- Computer Peripherals

- Automotive

- Personal Computers

- Toys/Games

- Educational Aids

- Warning Systems

- Security Systems

- Electronic Musical Instrume

- Aids to the Blind

- Narrow Bandwidth

- Communication Systems

| •                     |         |  |

|-----------------------|---------|--|

| GENERAL<br>INSTRUMENT | SP0256A |  |

#### OPERATION DESCRIPTION

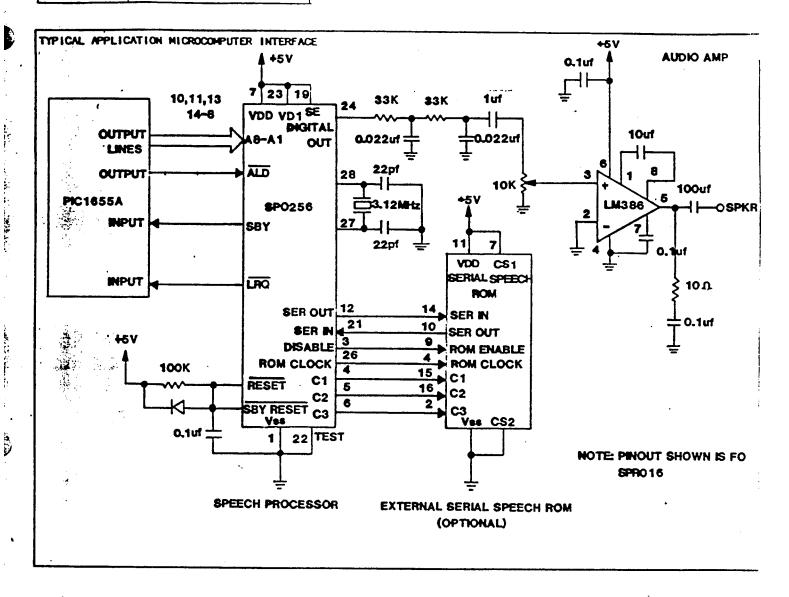

The addressing of the SP0256A is controlled by the address pins (A1-A8). Address Load (ALD), and Strobe Enable (SE). Speech data for the SP0256A may be stored within the internal 16K ROM and/or an external serial speech ROM.

There are two modes available for loading an address into the chip. Strobe Enable (SE) controls which mode will be used.

Mode O (SC=0). The speech processor will latch an address when any one (or more) address pin makes a low to high transition. All address lines must be returned to the low state prior to entering a new address. (Note: Address zero (0000 0000) is not a valid address in this mode of operation.) In order to best utilize this mode of operation, a vocabulary should consist of no more than eight individual words or phrases such that single address line transitions can be made. These words or phrases must be stored using the following entry point address: 1, 2, 4, 8, 16, 32, 64 and 128.

NOTE: There is a 2 byte overhead penalty paid for each dummy entry point between the entry points actually used.

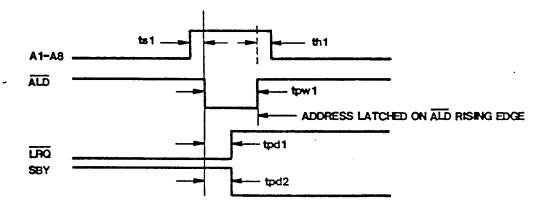

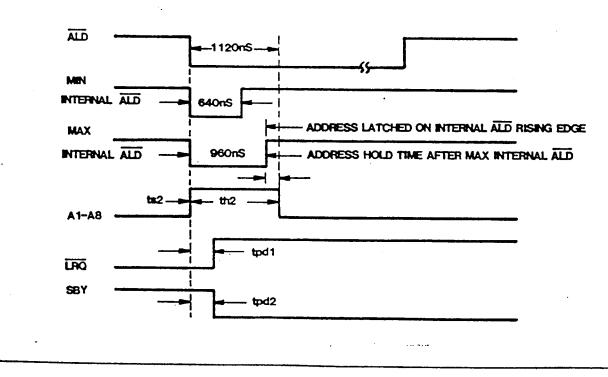

Mode 1 (SE=1). The SP0256A will latch an address using the ALD pin. The desired address is set up on the address bus (A1-A8) and then ALD is pulsed low. Any address can be loaded using this mode, but certain set up and hold times are required (refer to the timing diagrams for the specific times).

Iwo microprocessor interface pins are available for loading of addresses using mode 1. They are LRC and SBY. boad Request (LRC) tells the processor when the address input buffer is full. Standby (SBY) tells the processor that the chip has stapped talking and no new address has been loaded.

When LRQ is low, a new address may be loaded onto the address bus. Strobing ALD will cause the new address to be loaded and LRQ to go high. LRQ will return low when the address buffer is available to accept a new address. The SP0256A is capable of latching one new address while speaking the last utterance (word or phrase). The time between address load requests is variable, depending on the length of the utterance currently being spoken.

Standby (SBY) goes low when an address is loaded and will stay low until all internal instructions have been completed (i.e. the speech chip stops talking). If a second address has been loaded before the chip stops speaking the first utterance, SBY will stay low through the completion of the second utterance (ad infinitum).

The SP0256A may be partially powered down when SBY is high to conserve battery life, provided VD1 remains powered. During power down and power up, reset should be held low to ensure the proper reset condition. While the speech processor is in the partial power down state, the handshake control signals (ALD, SE, LRQ, and SBY) and the address bus are active. However, the SP0256A will not output the addressed speech data until after  $V_{\rm DD}$  is reapplied.

GENERAL INSTRUMENT

SP0256A

| GENERAL    |

|------------|

| INSTRUMENT |

# SP0256A

# PIN FUNCTIONS

| PIN NUMBER                        | NAME                             | FUNCTION                                                                                                                                                                                                                    |  |  |  |  |

|-----------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                                 | v <sub>ss</sub>                  | Ground .                                                                                                                                                                                                                    |  |  |  |  |

| 2                                 | RESET                            | A logic 0 resets that portion of the SP powered by $V_{DD}$ . Must be returned to logic 1 for normal operation.                                                                                                             |  |  |  |  |

| 3                                 | ROM DISABLE                      | For use with an external serial speech ROM a logic 1 disables the external ROM.                                                                                                                                             |  |  |  |  |

| 4, 5, 6                           | C1, C2, C3                       | Output control lines for use with an external serial speech ROM. Refer to the SPRO16 or SPR128 data sheet for details.                                                                                                      |  |  |  |  |

| 7                                 | v <sub>DD</sub>                  | Power supply for all portions of the SP except the microprocessor interface logic.                                                                                                                                          |  |  |  |  |

| 8                                 | ŚBY                              | STANDBY. A logic 1 output indicates that the SP inactive and V <sub>DD</sub> can be powered down external to conserve power. When the SP is reactivated an address being loaded, SBY will go to a logic                     |  |  |  |  |

| 9                                 | LRQ                              | LOAD REQUEST. LRQ is a logic 1 output whenever the input buffer is full. When LRQ goes to a logic 0, the input port may be loaded by placing the 8 address bits on A1-A8 and pulsing the ALD input.                         |  |  |  |  |

| 10, 11, 13, 14,<br>15, 16, 17, 18 | A8, A7, A6, A5<br>A4, A3, A2, A1 | 8 bit address which defines any one of 256 speech entry points.                                                                                                                                                             |  |  |  |  |

| 12                                | SER OUT                          | SERIAL ADDRESS OUT. This output transfers a 16-bit address serially to an external speech ROM.                                                                                                                              |  |  |  |  |

| 19                                | SE                               | STROBE ENABLE. Normally held in a logic 1 state. When tied to ground, ALD is disabled and the SP will automatically latch in the address on the input bus approximately 1 us after detecting a logic 1 on any address line. |  |  |  |  |

| 20                                | ALD                              | ADDRESS LOAD. A negative pulse on this input loads the 8 address bits into the input port. The negative edge of this pulse causes LRQ to go high.                                                                           |  |  |  |  |

| 21                                | SER IN                           | SERIAL IN. This is an 8-bit serial data input from an external speech ROM.                                                                                                                                                  |  |  |  |  |

GENERAL INSTRUMENT

SP0256A

| PIN NUMBER | NAME        | FUNCTION                                                                                                                            |

|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 22         | TEST        | This pin should be grounded for normal operation.                                                                                   |

| 23         | VD1         | Power supply for the microprocessor interface logic and controller.                                                                 |

| 24         | DIGITAL OUT | Pulse width modulated digital speech output which, when filtered by a 5KHz low pass filter and amplifier, will drive a loudspeaker. |

| 25         | SBY RESCT   | STANDBY RESET. A logic O resets the microprocessor interface logic and the address latches. Must be returned to logic 1             |

| 26         | ROM CLOCK   | This is a 1.56MHz clock output used to drive an external serial speech ROM.                                                         |

| 27         | OSC1        | XTAL IN. Input connection for a 3.12MHz crystal.                                                                                    |

| 28         | OSC2        | XTAL OUT. Output connection for a 3.12MHz crystal.                                                                                  |

# ELECTRICAL CHARACTERISTICS

| Maximum Ratings*                         |                |

|------------------------------------------|----------------|

| All pins with respect to V <sub>SS</sub> | -0.3 to 8.0V   |

| Storage Temperature                      | -25°C to 125°C |

## Standard Conditions

\*Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied: Operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Data labeled "Typical" is presented for design guidance only and is not guaranteed.

## DC CHARACTERISTICS/SP0256A

| Characteristic                          | Sym             | Min | Тур | Max             | Units | Conditions                                     |

|-----------------------------------------|-----------------|-----|-----|-----------------|-------|------------------------------------------------|

| Supply Voltage                          | $v_{DD}$        | 4.6 | -   | 7.0             | ٧     |                                                |

| $\mathcal{L}_{\mathbf{a}}^{\mathbf{b}}$ | V <sub>D1</sub> | 4.6 | -   | 7.0             | ٧     | ·                                              |

| ·                                       |                 |     |     | <u> </u>        |       |                                                |

|                                         | ł               |     |     | l               |       |                                                |

| Supply Current                          | I <sub>DD</sub> | -   | -   | 80              | mA    | 25°C no loads. Reset and SBY.                  |

|                                         | į               |     |     | 1               |       | Reset high. OSC1=3.12MHz. Al:                  |

|                                         |                 |     |     | ĺ               |       | other inputs floating.                         |

| •                                       |                 |     |     | }               |       | 95mA MAX at 0°C                                |

|                                         | 1.              |     |     |                 |       | •                                              |

|                                         | I <sub>D1</sub> | -   | -   | 25              | mA    | 25°C same as above                             |

|                                         |                 |     |     | ļ               |       | 29.OmA MAX at O°C                              |

|                                         | ]               |     |     |                 |       |                                                |

| INPUTS                                  |                 |     |     |                 |       |                                                |

| A1-A8, ALD, SERIN, TEST, SE             |                 |     |     |                 |       |                                                |

| LOGIC O                                 | VIL             | 0.0 | _   | 0.6             | v     |                                                |

| LOGIC 1                                 | v <sub>IH</sub> | 2.4 | _   | V <sub>D1</sub> | v     |                                                |

| CAPACITANCE                             | CIN             |     | _   | 10              | pf    | O volts bias, f=3.12 MHz                       |

| LEAKAGE                                 | IL              | -   | -   | +10             | ua.   | V <sub>PIN</sub> = 7.0V Other Pins = 0.0V      |

| <b>₹</b> (%)                            |                 |     | !   |                 |       | PIN = 110. CO.02 12.00 = 010.                  |

|                                         |                 |     |     |                 |       |                                                |

| RESET, SBY RESET                        | 1               |     |     |                 |       |                                                |

| LOGIC O                                 | VRSIL           | 0.0 | -   | 0.6             | ٧     | V <sub>RSIH</sub> MIN at V <sub>D1</sub> =4.6V |

| LOGIC 1                                 | VRSIH           | 4.0 | -   | V <sub>D1</sub> | ٧     | VRSIH MIN increases by                         |

|                                         |                 |     |     |                 |       | .2V per volt of $v_{\text{D1}}$ increase       |

|                                         |                 |     |     |                 |       |                                                |

| OUTPUTS                                 |                 |     |     |                 |       |                                                |

| SBY, Digital Out, C1, C2, C3,           |                 |     |     |                 |       |                                                |

| LRQ, ROM DIS, ROM CLK,                  |                 |     |     |                 |       |                                                |

| SEROUT                                  |                 |     |     |                 |       |                                                |

| LOGIC O                                 | V <sub>OL</sub> | 0.0 | _   | 0.6             | v     | IOL=0.72ma (2LS TTL Loads)                     |

| LOGIC 1                                 | V <sub>OH</sub> | 2.5 | -   | V <sub>D1</sub> | v     | I <sub>DH</sub> =-50ua (2LS TIL Loads)         |

|                                         | Un              | 1   |     | וטי             | ,     | TUH>000 (200 File COMOS)                       |

| OSCILLATOR                              |                 | 1   |     |                 |       |                                                |

| OSC 2 (Output)                          |                 |     |     |                 |       | When driven from external inpu                 |

| FOGIC O                                 | v <sub>OL</sub> | 0.0 | -   | 1.0             | ٧     | • OSC1 (Input)=4.00V MIN at                    |

|                                         |                 |     |     |                 |       | V <sub>D1</sub> =4.60V                         |

| LOGIC 1                                 | v <sub>OH</sub> | 2.5 | -   | V <sub>D1</sub> | ٧     | OSC1 (Input)=0.60V MAX                         |

| GENERAL<br>INSTRUMENT | SP0256A |

|-----------------------|---------|

|-----------------------|---------|

| CHARACTERISTICS - AC          | SYM                                            | MIN                         | TYP              | MAX                         | UNITS                | CONDITIONS                             |

|-------------------------------|------------------------------------------------|-----------------------------|------------------|-----------------------------|----------------------|----------------------------------------|

| ALD A1-A8 Set Up Hold LRQ SBY | t <sub>pw1</sub><br>ts1<br>th1<br>tpd1<br>tpd2 | 200<br>160<br>160<br>-<br>- | -<br>-<br>-<br>- | 960<br>-<br>-<br>300<br>300 | ns<br>ns<br>ns<br>ns | 200 <u>&lt;</u> ALD <u>&lt;</u> 960 ns |

| CHARACTERISTICS - AC        | SYM                                                    | MIN            | TYP | MAX           | UNITS          | CONDITIONS   |

|-----------------------------|--------------------------------------------------------|----------------|-----|---------------|----------------|--------------|

| A1-A8 Set Up<br>Hold<br>LRQ | t <sub>s2</sub><br>t <sub>h2</sub><br>t <sub>pd1</sub> | 0<br>1120<br>- | -   | -<br>-<br>300 | ns<br>ns<br>ns | ALD > 960 ns |

| SBY                         | t <sub>pd2</sub>                                       | -              | -   | 300           | ns             |              |

GENERAL SP0256A

| CHARACTERISTICS - AC                 | SYM                | MIN       | TYP       | MAX      | UNITS                                 | CONDITIONS                            |

|--------------------------------------|--------------------|-----------|-----------|----------|---------------------------------------|---------------------------------------|

| CRQ                                  | t <sub>pd3</sub> . | 16.67     | -         | 33.3     | μS                                    | Address Buffer ready for next load.   |

| TYPICAL TIMING SEQUENCE              |                    |           |           | •        |                                       |                                       |

| •                                    |                    |           |           |          |                                       |                                       |

|                                      |                    |           |           |          |                                       |                                       |

|                                      |                    | ·····     | <u> </u>  |          |                                       |                                       |

| SBY RESET,                           |                    |           |           |          |                                       |                                       |

| ALD -                                |                    |           |           |          |                                       |                                       |

| ALL -                                |                    |           |           |          | · · · · · · · · · · · · · · · · · · · |                                       |

|                                      | لــا               | !         | / '       |          |                                       |                                       |

|                                      |                    |           |           |          | AN LOAD DATA<br>Q GOES LOW.           |                                       |

|                                      |                    | 1         |           |          | ia does toii.                         |                                       |

| <u> </u>                             | — tpd              | 3         | <u> </u>  |          |                                       | -START OF SECOND SEQUENCE.            |

| <u>L</u>                             |                    | L         |           |          |                                       |                                       |

| SBY -                                |                    |           |           |          |                                       | <del></del>                           |

|                                      |                    | START OF  | FIRST SPE | CH SEQUE | NCE.                                  |                                       |

|                                      |                    |           |           |          |                                       | •                                     |

|                                      |                    |           | •         |          |                                       |                                       |

|                                      |                    |           |           |          |                                       |                                       |

| + <b>v</b> ,                         |                    |           |           |          |                                       |                                       |

|                                      |                    |           |           |          |                                       |                                       |

| CUADACTERICTICS                      | T - 21             |           | T         |          | ·                                     | · · · · · · · · · · · · · · · · · · · |

| CHARACTERISTICS - AC                 | SYM                | MIN       | TYP       | MAX      | UNITS                                 | CONDITIONS                            |

| Clock                                | F                  | -         | 3.120     | -        | MHz                                   | Crystal                               |

| Clock Duty Cycle<br>Reset, SBY Reset | -                  | 49        | -         | 52       | *                                     | Osc., driven from                     |

| neset, sor neset                     | t <sub>pw2</sub>   | 25        |           | -        | μs                                    | external                              |

|                                      |                    |           |           |          |                                       |                                       |

|                                      |                    |           |           |          |                                       |                                       |

|                                      |                    |           |           |          |                                       |                                       |

|                                      | SBY RE             | SET,RESET | i         |          |                                       |                                       |

|                                      |                    |           |           |          | tpw2                                  |                                       |

|                                      |                    |           |           |          |                                       |                                       |

|                                      |                    |           |           |          |                                       |                                       |

|                                      |                    |           |           |          | * 14 T. 14 .                          | •                                     |

|                                      |                    |           |           |          |                                       |                                       |

GENERAL INSTRUMENT SP0256A

TYPICAL APPLICATION STAND ALONE CONFIGURATION AUDIO AMP 0.14 **+5**V 23 1uf DIGITAL 10uf A6 OUT A5 15 **S**P0256 A4 16 A3 17 A2 18 SPKR A1 SBY 10K 10Ω 22pf OSC 2 28 **+5**V 100K 2 RESET OSC 1 27 25 SBY RESET 22pf VSS TEST 0.1uf \*Diode possibly necessary if power is turned off then on in less than 50 ms.